Chapter 05 CPU 성능 향상 기법

1. 빠른 CPU를 위한 설계 기법

Key Word: 클럭 / 코어 / 멀티코어 / 스레드 / 멀티스레드

클럭

04장

- (컴퓨터 부품들) '클럭 신호'에 맞춰 일사불란하게 움직임

- (CPU) '명령어 사이클'이라는 정해진 흐름에 맞춰 명령어 실행

클럭 신호 빠르게 반복 -> CPU를 비롯한 컴퓨터 부품들 그만큼 빠른 박자에 맞춰 움직임

=> 클럭 속도 ↑ -> (CPU) 명령어 사이클 더 빠르게 반복, 다른 부품 발맞춰 더 빠르게 작동

클럭 속도 ↑ CPU는 일반적으로 성능이 좋음

=> 클럭 속도는 CPU 속도 단위로 간주되기도 함

클럭 속도

- 헤르츠(Hz) 단위로 측정

- 진동수/시간

- 1초에 클럭이 몇 번 반복되는지를 나타냄

- 클럭이 '똑-딱-' 1초에 1번 반복 -> CPU 클럭 속도: 1Hz / 1초에 100번 반복 -> CPU 클럭 속도: 100Hz

- 무작정 높이면 발열 문제 심각해짐

=> 클럭 속도 높이는 것은 CPU 빠르게 만듦 But, 클럭 속도만으로 CPU 성능 올리는 것에 한계(발열)

-> CPU 코어 or 스레드 수 ↑ ~> CPU 성능 ↑

CPU: 기본 클럭 속도(Base) / 최대 클럭 속도(Max)

클럭 속도는 일정 X

계속 일정한 클럭 속도 유지하기보다 고성능 요하는 순간 -> 클럭 속도 높임

오버클럭킹(overclocking): 최대 클럭 속도를 강제로 더 끌어올리는 기법

코어와 멀티코어

CPU

- 명령어를 실행하는 부품

- (오늘날) 명령어를 실행하는 부품을 여러 개 포함하는 부품

- 8코어(core) = 명령어를 실행하는 부품 8개 포함

코어(core)

CPU 내에서 명령어를 실행하는 부품, 여러 개 있을 수 있음

멀티코어(multi-core) CPU = 멀티코어 프로세서

- 코어를 여러 개 포함하고 있는 CPU

- CPU 내에 명령어 처리하는 일꾼 여러 명 있는 것

- 처리 속도: 멀티 코어 > 단일 코어

- 클럭 속도 1.9GHz인 멀티코어 CPU > 클럭 속도 2.4GHz인 단일 코어 CPU

<CPU 안에 코어가 몇 개 포함되어 있는지 -> CPU 종류>

- 싱글코어(single-core): 코어 1

- 듀얼코어(dual-core): 코어 2

- 트리플코어(triple-core): 코어 3

- 쿼드코어(quad-core): 코어 4

- 헥사코어(hexa-core): 코어 6

- 옥타코어(octa-core): 코어 8

- 데카코어(deca-core): 코어 10

- 도데카코어(dodeca-core): 코어 12

CPU의 연산 속도가 코어 수에 비례하여 증가 X

처리하고자 하는 작업량보다 코어 수가 지나치게 많아도 성능에 크게 영향 X

=> 코어마다 처리할 명령어들 얼마나 적절하게 분배하느냐 -> 연산 속도 크게 달라짐

트렌지스터 모여서 코어 (약 100조개)

Q: 같은 가격인데 왜 싱글, 듀어 코어 이렇게 만들까?

A: 둘 중 하나 고장나면 듀얼코어가 아니라 싱글코어로 판매(불량률 ↑)

맥스 스펙이 듀얼 코어 -> 하나 망가짐 => 하나 끄고 싱글 코어로 판매

i7 중에 8, 16코어 -> 16코어에서 망가지면 8코어로 판매

16개를 기본으로 만드는 것도 있지만 한 번에 16개가 다 죽을 수 있음

or 이전 세대 8코어 잘 만들었으면 2개 합쳐서 16코어 만드는 경우(현재 8코어를 기준으로 만듦)

스레드와 멀티스레드

스레드(thread): 실행 흐름의 단위

CPU에서 사용되는 스레드 != 프로그래밍에서 사용되는 스레드

- 하드웨적 스레드(CPU): 하나의 코어가 동시에 처리하는 명령어 단위

- 소프트웨어적 스레드(프로그래밍): 하나의 프로그램에서 독립적으로 실행되는 단위

하드웨어적 스레드(하드웨어 스레드) = 논리 프로세서((logical processor)

- 하나의 코어가 동시에 처리하는 명령어 단위

- CPU에서 사용하는 스레드

- 1코어 1스레드 CPU = 명령어 실행하는 부품 하나, 한 번에 하나씩 명령어 실행하는 CPU

- 여러 스레드를 지원하는 CPU = 하나의 코어로도 여러 개의 명령어 동시에 실행할 수 있음

=> 멀티스레드 프로세서

-> 하이퍼스레딩(hyper-threading): 인텔의 멀티스레드 기술

- ex. 2코어 4스레드 CPU = 명령어를 실행하는 부품을 2개 포함, 한 번에 4개 명령어를 처리할 수 있는 CPU

- ex. 8코어 16스레드 CPU: 명령어를 실행하는 부품을 8개 포함, 한 번에 16개 명령어 처리할 수 있는 CPU

= 코어 하나당 2개의 하드웨어 스레드 처리

멀티스레드(multithread) 프로세서 = 멀티스레드 CPU

- 실제로 설계하는 일 매우 복잡, 큰 핵심은 레지스터

- 하나의 코어로 여러 명령어 동시에 처리할 수 있는 CPU

-> 하나의 명령어 처리하기 위해 꼭 필요한 레지스터 세트(레지스터를 여러 개) 가지고 있으면 됨

(프로그램 카운터, 스택 포인터, 데이터 버퍼 레지스터, 데이터 주소 레지스터)- ex. 프로그램 카운터 2개 -> 메모리에서 가져올 명령어 주소 2개 지정

- ex. 스택 포인터 2개 -> 2개의 스택 관리할 수 있음

2코어 4스레드 CPU: 한 번에 4개의 명령어 처리 => (프로그램 입장) 1번에 1개 명령어 처리하는 CPU 4개

=> 하드웨어 스레드 = 논리 프로세서

소프트웨어적 스레드(스레드)

- 하나의 프로그램에서 독립적으로 실행되는 단위

- 프로그래밍 언어 or 운영체제 학습할 때 접하는 스레드

- 하나의 프로그램은 실행되는 과정에서 한 부분만 실행 or 여러 부분 동시 실행

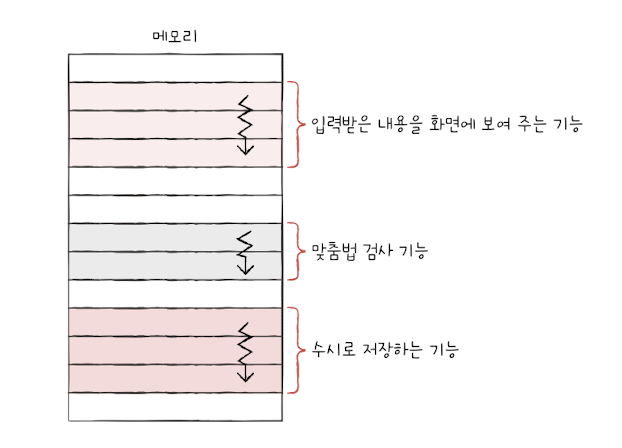

<워드 프로세서 프로그램 개발> 기능 동시에 수행되기를 원함

1. 사용자로부터 입력받은 내용을 화면에 보여 주는 기능

2. 사용자가 입력한 내용이 맞춤법에 맞는지 검사하는 기능

3. 사용자가 입력한 내용 수시로 저장하는 기능

=> 기능을 작동시키는 코드를 각각의 스레드로 만들면 동시에 실행할 수 있음

<정리>

- 코어: 명령어를 실행할 수 있는 하드웨어 부품

- 멀티코어 프로세서: 명령어를 실행할 수 있는 하드웨어 부품이 CPU 안에 2개 이상 있는 CPU

- 스레드: 명령어를 실행하는 단위

- 멀티스레드 프로세서: 하나의 코어로 여러 개의 명령어를 동시에 실행할 수 있는 CPU

2. 명령어 병렬 처리 기법

Key Word: 명령어 파이프라인 / 슈퍼스칼라 / 비순차적 명령어 처리 기법

명령어 병렬 처리 기법(ILP: Instruction-Level Parallelism)

- 명령어 빠르고 효율적으로 처리 -> CPU 쉬지 않고 작동시킴

- 명령어 파이프 라이닝 / 슈퍼스칼라 / 비순차적 명령어 처리

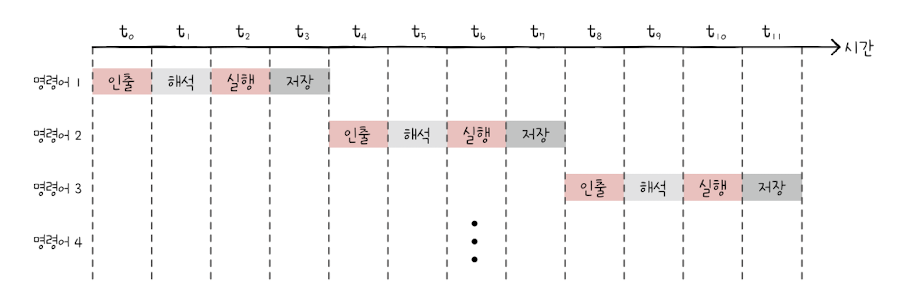

명령어 파이프라인

명령어 처리 과정 -> 클럭 단위로 나눔

- 명령어 인출(Instruction Fetch)

- 명령어 해석(Instruction Decode)

- 명령어 실행(Execute Instruction)

- 결과 저장(Write Back)

전공서에 따라

- 명령어 인출 -> 명령어 실행

- 명령어 인출 -> 해석 -> 실행 -> 메모리 접근 -> 결과 저장

단계가 겹치지 않는다면 CPU는 각 단계를 동시에 실행할 수 O

-> 명령어 겹쳐서 수행 > 하나하나 실행 => 효율적 처리 가능

명령어 파이프라이닝(instruction pipelining)

- 명령어들을 명령어 파이프라인(instruction pipeline)에 넣고 동시에 처리하는 기법

- 동시에 여러 개의 명령어를 겹쳐 실행하는 기법

- (+) ↑ 성능 가져옴

- (-) 파이프라인 위협(pipeline hazard): 특정 상황에서는 성능 향상에 실패하는 경우

- 데이터 위험(data hazard): 명령어 간 데이터 의존성에 의해 발생

- 명령어 1: R1 <- R2 + R3 // R2 레지스터 값, R3 레지스터 더한 값 R1에 저장

명령어 2: R4 <- R1 + R5 // R1 레지스터 값, R5 레지스터 더한 값 R4에 저장

=> 명령어 2는 명령어 1에 의존적 -> 파이프라인 제대로 작동 X

=> (방법) 저장된 곳 확인(ex. R1, R4)

- 명령어 1: R1 <- R2 + R3 // R2 레지스터 값, R3 레지스터 더한 값 R1에 저장

- 제어 위험(control hazard): 분기 등으로 인한 프로그램 카운터의 갑작스러운 변화에 의해 발생

- 프로그램 카운터) 현재 실행 중인 명령어의 다음 주소로 갱신

But, IF. 프로그램 실행 흐름 바뀌어 명령어가 실행되면서 프로그램 카운터 값에 갑작스러운 변화

-> 미리 처리 중이던 명령어 쓸모 X - 분기 예측(branch prediction): 프로그램이 어디로 분기할지 미리 예측 후 그 주소 인출하는 기술

- 프로그램 카운터) 현재 실행 중인 명령어의 다음 주소로 갱신

- 구조적 위험(stuctural hazard) = 자원 위험(resource hazard)

: 명령어들 겹쳐 실행하는 과정에서 서로 다른 명령어가 동시에 같은 CPU 부품 사용하려고 할 때 발생

- 데이터 위험(data hazard): 명령어 간 데이터 의존성에 의해 발생

슈퍼스칼라(superscalar)

- CPU 내부에 여러 개의 명령어 파이프라인을 포한한 구조

- 여러 개의 명령어 파이프라인을 두는 기법

- 공장 생산 라인 여러 개 두는 것

- 명령어 파이프라인 하나만 두는 것 = 공장 생산 라인 한 개 두는 것

- 슈퍼스칼라 프로세서 = 슈퍼스칼라 CPU

- 슈퍼스칼라 구조로 명령어 처리가 가능한 CPU

- 매 클럭 주기마다 동시에 여러 명령어 인출, 실행할 수 있어야 함

=> 파이프라인 2개(명령어1, 3, 5, 7/ 명령어 2, 4, 6, 8)

비순차적 명령어 처리(OoOE: Out-of-order execution)

- 명령어들을 순차적으로 실행하지 않는 기법

- 명령어의 합법적인 새치기

- 파이프라인의 중단 방지 위해 명령어를 순차적으로 처리 X 명령어 병렬 처리 기법

- 명령어 파이프라이닝, 슈퍼스칼라 기법: 순차적 명령어 처리

But, 예상 X 문제(ex. 파이프라인 위험) -> 명령어 곧바로 처리 X

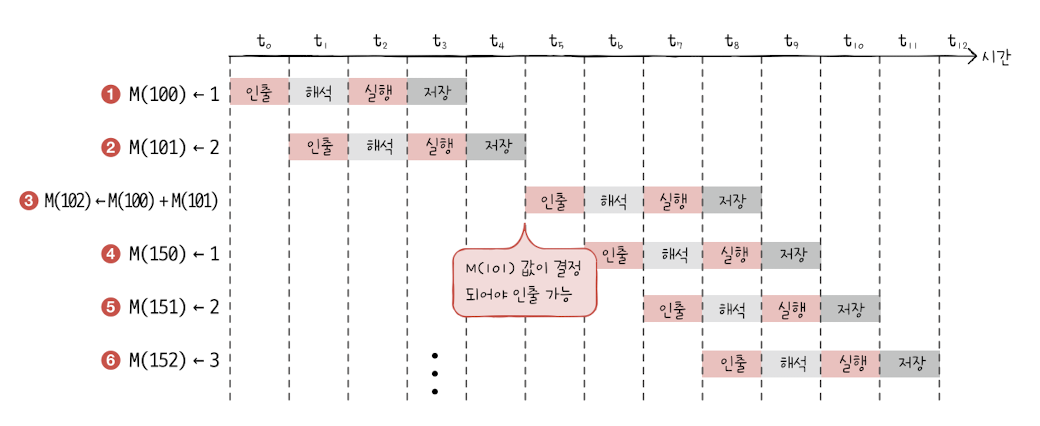

ex. M(N): 메모리 N번지 / M(N) <- N: 메모리 N번지에 M을 저장

1. M(100) <- 1

2. M(101) <- 2

3. M(102) <- M(100) + M(101)

4. M(150) <- 1

5. M(151) <- 2

6. M(152) <- 3

=> 3번 명령어 실행 -> M(100)값, M(101)값 결정 되어야 함 => 1, 2번 명령어 실행 끝날 때까지 기다려야 함

-> 2번 끝날 때까지 3, 4, 5, 6 대기

But, 순서 바꿔 처리해도 수행 결과 영향 X 명령어 O

=> 1 -> 2 -> 4 -> 5 -> 6 -> 3

=> 비순차적 명령어 처리가 가능한 CPU

-> 어떤 명령어와 데이터 의존성을 가지고 있는지, 순서를 바꿔 실행할 수 있는 명령어에는 어떤 것이 있는지 판단할 수 있어야 함

3. CISC와 RISC

Key Word: ISA / CISC / RISC

명령어 파이프라이닝, 슈퍼스칼라 기법을 실제로 CPU에 적용 = CPU가 파이프라이닝, 슈퍼스칼라 기법 효과적으로 사용

-> 명령어가 파이프라이닝에 최적화되어 있어야 함 = CPU가 인축, 해석, 실행하는 명령어가 파이프라이닝 하기 쉽게 생겨야 함

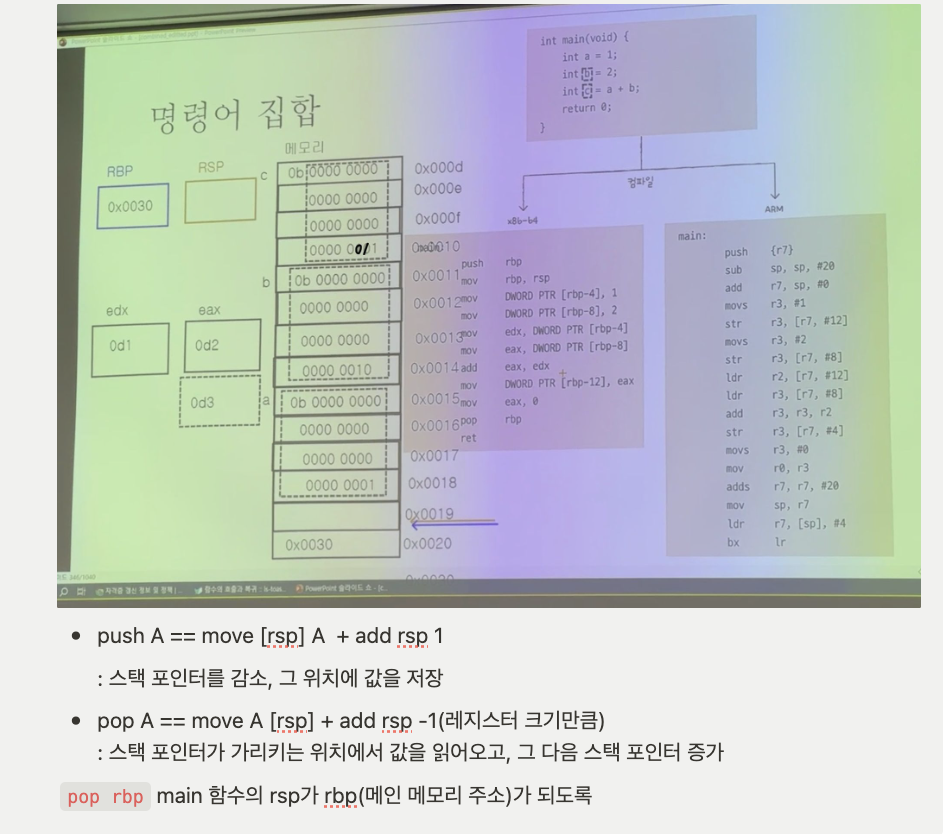

ISA: CPU의 언어

- CISC

- RISC

03장

- 명령어의 생김새, 주소 지정 방식 학습

- CPU: 명령어 실행

Q: 모든 CPU는 똑같이 생긴 명령어 실행? 수많은 CPU 제조사, CPU마다 규격과 기능, 만듦새 다름

모든 CPU가 이해하고 실행하는 명령어 다 똑같이 생김?

A: 그렇지 않음

명령어의 기본적인 구조와 작동원리 비슷하지만,

명령어의 세세한 생김새, 명령어로 할 수 있는 연산, 주소 지정 방식 등은 CPU마다 다름

명령어 집합(instruction set) = 명령어 집합 구조(ISA; Instruction Set Architecture)

- CPU가 이해할 수 있는 명령어들의 모음

- CPU마다 ISA가 다를 수 있음

- CPU의 언어, 하드웨어가 소프트웨를 어떻게 이해할지에 대한 약속

구조: CPU가 어떤 명령어를 이해하는지 -> 컴퓨터 구조 및 설계 방식 달라짐

인텔의 노트북 속 CPU: x86 or x86-64ISA 이해

애플의 아이폰 속 CPU: ARM ISA 이해

x86 or x86-64ISA != ARM

-> 인텔 CPU를 사용하는 컴퓨터와 아이폰은 서로의 명령어 이해 X

실행 파일은 명령어로 이뤄짐, 서로의 컴퓨터가 이해할 수 있는 명령어가 다름

x86: 32비트용/ x86-64: 64비트용 x86 ISA

스택: 메모리의 높은 주소 → 낮은 주소

x86-64(CISC) < ARM(RISC) 레지스터 사용 ⇒ x86-64가 더 복잡, 전력 ↑

ex. x86-64: 자전거/ ARM: 바퀴, 의자,...

But, ARM 한계: CPU로 쪼개서 연산

CPU로 계산하는데 한계 -> GPU(가속기)

=> 자주 쓰는 특정 연산 -> 하드웨어로 회로 더 만드는 것이 전력 ↓ 속도 ↑

- 어셈블리어: 명령어를 읽기 편하게 표현한 언어(03장)

- ISA가 다름 = CPU가 이해할 수 있는 명령어가 다름 -> 어셈블리어 달라짐

=> 같은 소스 코드로 만들어진 같은 프로그램, ISA가 다르면 CPU가 이해할 수 있는 명령어, 어셈블리어 달라짐

- ISA가 다름 = CPU가 이해할 수 있는 명령어가 다름 -> 어셈블리어 달라짐

- ISA가 같은 CPU -> 서로의 명령어 이해 O

- ISA가 다른 CPU -> 서로의 명령어 이해 X

- 제어장치가 명령어 해석하는 방식, 사용되는 레지스터의 종류와 개수, 메모리 관리 방법 등 많은 것이 달라짐

-> CPU 하드웨어 설계에도 영향 미침

- 제어장치가 명령어 해석하는 방식, 사용되는 레지스터의 종류와 개수, 메모리 관리 방법 등 많은 것이 달라짐

CISC(Complex Instruction Set Computer)

- 복잡한 명령어 집합을 활용하는 컴퓨터(CPU)

- 명령어 형태, 크기 다양한 가변 길이 명령어 활용

- 다양한 메모리에 접근하는 주소 지정 방식

- 복잡하고 다양한 명령어들을 활용하는 CPU 설계 방식

- 복잡하고 다양한 수의 가변 길이 명령어 집합 활용

- 상대적으로 적은 수의 명령어로 프로그램 실행 -> (+) 메모리 공간 절약

= 컴파일된 프로그램의 크기가 작음 - (-) 명령어 크기, 실행되기까지 시간 일정 X = 규격화 X 명령어

- (-) 명령어 하나 실행하는 데 여러 클럭 주기 필요

=> 파이프라이닝 어려움 - (-) 복잡한 명령어 사용 빈도 ↓

- 상대적으로 적은 수의 명령어로 프로그램 실행 -> (+) 메모리 공간 절약

- 대표적인 CISC 기반의 ISA: x86, x86-64

CISC의 한계가 준 교훈

- 빠른 처리 -> 명령어 파이프라인을 십분 활용해야 함

원활한 파이프라이닝 -> 명령어 길이와 수행 시간 ↓ + 규격화 - 어차피 자주 쓰이는 명령어만 줄곧 사용

복잡한 기능 지원하는 명령어 추가 < 자주 쓰이는 기본적인 명령어 -> 작고 빠르게 만드는 것

=> RISC 등장

RISC(Reduced Instruction Set Computer)

- 명령어의 종류 ↓ (vs. CISC)

- 명령어 길이 ↓ + 규격화 (vs. CISC)

- 되도록 1클럭 내외로 실행되는 명령어 지향

=> 명령어 파이프라이닝에 최적화 - 단순하고 적은 수의 고정 길이 명령어 집합 활용

- 메모리에 직접 접근하는 명령어: load, store 2개로 제한

- 메모리 접근 단순화, 최소화

- CISC보다 주소 지정 방식의 종류가 ↓ 경우 ↑

- load-store 구조

- 레지스터 적극적으로 활용

- CISC보다 레지스터를 이용한 연산 ↑

- 일반적인 경우보다 범용 레지스터 개수 ↑

- But, 사용 가능한 명령어 개수 CISC보다 ↓

- CISC보다 ↑ 명령으로 프로그램 작동시킴

<정리>

| CISC | RISC |

| 복잡하고 다양한 명령어 | 단순하고 적은 명령어 |

| 가변 길이 명령어 | 고정 길이 명령어 |

| 다양한 주소 지정 방식 | 적은 주소 지정 방식 |

| 프로그램을 이루는 명령어의 수 ↓ | 프로그램을 이루는 명령어의 수 ↑ |

| 여러 클럭에 걸쳐 명령어 수행 | 1클럭 내외로 명령어 수행 |

| 파이프라이닝하기 어려움 | 파이프라이닝하기 쉬움 |

출처

[한빛미디어] 혼자 공부하는 컴퓨터 구조+운영체제

좋은 개발자는 컴퓨터를 분석의 대상으로 바라볼 뿐, 두려워하지 않는다!‘전공서가 너무 어려워서 쉽게 배우고 싶을 때’, ‘개발자가 되고 싶은데 뭐부터 봐야 하는지 모를 때’ ‘기술 면접

hongong.hanbit.co.kr

'📓 > 컴퓨터구조 | 운영체제' 카테고리의 다른 글

| [혼자 공부하는 컴퓨터구조+운영체제] Chapter 07 보조기억장치 (0) | 2024.01.08 |

|---|---|

| [혼자 공부하는 컴퓨터구조+운영체제] Chapter 06 메모리와 캐시 메모리 (0) | 2024.01.08 |

| [혼자 공부하는 컴퓨터구조+운영체제] Chapter 04 CPU의 작동 원리 (0) | 2024.01.08 |

| [혼자 공부하는 컴퓨터구조+운영체제] Chapter 03 명령어 (0) | 2024.01.05 |

| [혼자 공부하는 컴퓨터구조+운영체제] Chapter 02 데이터 (0) | 2024.01.05 |